# Sistem Proteksi *Power Supply* Modul Praktikum Teknik Digital

## Anwar Mujadin

Program Studi Teknik Elektro, Fakultas Sain dan Teknologi Universitas Al Azhar Indonesia, Jl. Sisingamangaraja, Jakarta 12110

Penulis untuk Korespondensi/E-mail: amujadin@uai.ac.id

Abstrak – Dalam melakukan praktikum teknik digital berbasis protoboard kadangkala pihak pengguna melakukan kesalahan fatal yaitu terjadi hubung singkat power supply dalam interkoneksi. Untuk menghindari kerusakan power supply akibat hubung singkat dalam modul praktikum digital, diperlukan sebuah rangkaian elektronika yang mampu mendeteksi dan memutus arus sumber (power supply) dengan segera pada saat terjadi hubung singkat. Modul praktikum teknik digital dalam penelitian ini telah dilengkapi dengan sistem proteksi power supply dari hubung singkat dengan waktu tanggap kurang dari 5 ms, menggunakan teknis waktu jeda pengosongan kapasitor dan opamp pembanding tegangan.

Abstract – When conducting experiments practicum in digital protoboard base project, users often made a fatal mistake that cause short circuit interconnection. To avoid damaging the power supply of experiment module (hardware), it requires an electronic circuit that is able to detect and cut off the main power supply immediately. In research the modular lab has been equipped with an electronics short circuit protection system with a response time of less than 5 ms, using capacitor discharge and opamp voltage comparator technique.

**Keyword** – RC Transient, Power Supply Protection Systems, Bypass Filter Capacitor.

#### **PENDAHULUAN**

tonggak beberapa perkembangan memberi teknologi yang secara nyata sumbangsih terhadap perkembangan teknologi informasi dan komunikasi (TIK), vaitu temuan rangkaian terpadu elektronik berbasis digital. Konvergensi telekomunikasi komputasi multimedia adalah ciri abad ke-21. Dimana pada abad ke-18 terjadi revolusi industri menjadikan mesin-mesin sebagai pengganti 'otot' manusia, maka pada revolusi digital menciptakan mesinmesin sebagai pengganti 'otak' manusia [1].

Setelah dikeluarkannya mikrokontroler oleh para pabrikan dengan harga yang sangat terjangkau berikut dengan *software development* (gratis), menjadi peluang para pelajar maupun para penggemar elektronika untuk mempelajari lebih jauh mengenai ilmu teknik digital diera TIK ini. Mempelajari teknik digital perlu didukung oleh peralatan yang memadai sebagai bahan latihan, baik itu dilakukan di rumah maupun di laboratorium.

Dalam penelitian ini telah dirancang bangun sebuah modul pelatihan teknik digital terintegrasi dengan peralatan ukur dan pendukung dalam satu paket modul. Modul ini juga dapat dimanfaatkan oleh para lembaga pelatihan anak putus sekolah (pendidikan non formal) seperti di balai latihan kerja Indonesia (BLKI).

Modul pelatihan ini telah dilengkapi dengan fitur pendukung latihan seperti: 2 digit seven segment scanning, 1 digit seven segment, 1 segment dotmatrix 7X5 scanning, 10 Bar LED, LCD 2X16, 3x4 matrix keypad, 8 debouncing logic trigger, 8 step logic switch, 8 bouncing logic switch, 1-1MHz square wave generator, speaker dan buzzer.

Modul pelatihan teknik digital dalam penelitian ini dirancang berukuran mainboard 20 cm x 15 cm dilengkapi dengan R Shunt 0.5  $\Omega$  dan 1  $\Omega$  (5W) yang sangat efektif untuk penyaluran enegi listrik dan kompensasi suhu akibat desipasi daya berlebih. R Shunt berfungsi ganda juga sebagai pengosong kapasitor, bersinergi dengan opamp komparasi, mampu mendeteksi dan mengamankan power

supply utama dari kerusakan akibat short circuit dalam orde kurang dari 5 ms (0.1ms-1ms). Dalam tulisan ini akan dibahas lebih lanjut mengenai sistem proteksi power supply dari dari bahaya hubung singkat.

#### TINJAUAN PUSTAKA

Dalam tinjauan pustaka dibahas mengenai respon rangkaian seri RC dari unit step tegangan, *bypass filter*, transistor sebagai pengendali relay, dan opamp sebagai pembanding tegangan:

# Respon Rangkaian Seri RC dari Fungsi Step

#### Tegangan Arus Searah (Direct Current)

Pengisian dan pengosongan kapasitor ditetapkan pada tegangan perubahan tergangan kapasitor akibat perubahan arus tiap satuan waktu yang dapat di diformulasikan dengan [2]:

$$V_{C} = \frac{1}{C} \int i \frac{dv}{dt}$$

(2.1)

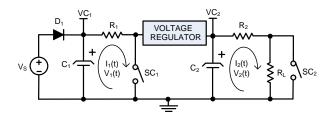

Pengosongan kapasitor sebagai akibat terjadinya hubung singkat dengan rangkaian diperlihatkan pada Gambar.1 berikut:

Gambar.1 Pengosongan kapasitor akibat hubung singkat.

Dari Gambar.1,  $R_1$  dan  $R_2$  adalah resistor R shunt yang nilainya antara 0.5-1  $\Omega$  dengan kemampuan menyalurkan daya lebih dari 5 Watt, tegangan jatuh pada beban ( $R_L$ ) mendekati  $VC_2$  (tegangan pada kapasitor 2), dan tegangan yang masuk kedalam voltage regulator mendekati  $VC_1$ = $V_S$ -0.7 V (Tegangan sumber dikurangi tegangan arus maju dioda silikon). D1 selain berfungsi sebagai proteksi dari kesalahan polaritas juga sebagai *time delay of voltage drop*.

SC<sub>2</sub> adalah notasi saklar apabila beban (R<sub>L</sub>) terjadi short circuit (SC) diposisi beban, sedangkan SC<sub>1</sub> adalah notasi saklar apabila voltage regulator drop

mendekati nol (ground) pada saat  $R_L$  ( $SC_2$ ) terhubung singkat. Pada kenyataanya antara  $SC_2$  dan  $SC_1$  memiliki perbedaan waktu beberapa milidetik dimana waktu tunda  $SC_2$  lebih cepat dibandingkan  $SC_1$ .

Pada saat terjadi hubung singkat beban  $(R_L)$  diilustrasikan dengan  $SC_2$  tertutup, maka tejadi pengosongan kapasitor  $C_2$ . Tegangan  $VC_2$  akan turun (transient) melaui  $R_2$   $(R_L=0\ \Omega)$  dengan perubahan arus sebesar  $I_2(t)$ , Perubahan tegangan  $VC_2$  tiap satuan waktu dapat diformulasikan sebagai [2]:

$$\frac{1}{C_2} \int I_2 dt + R_2 I_2 = 0 \quad \text{atau} \quad \frac{1}{C_2} \int I_2 dt = -R_2 I_2$$

(2.2)

$$\frac{I_2}{C_2} = -R_2 \cdot \frac{dI_2}{dt} \quad \text{atau} \quad \frac{dI_2}{I_2} = -\frac{dt}{R_2 C_2} \quad \text{(turunkan satu}$$

kali)

$$\int \frac{dI_2}{I_2} = -\int \frac{dt}{R_2 C_2}$$

(integralkan satu

kali)

(2.3)

$$\ln(I_2) = -\frac{t}{R_2 C_2} + k$$

$$I_2 = e^{(-\frac{t}{R_2 C_2} + k)} \text{ atau } I_2 = e^{-(\frac{t}{R_2 C_2})} e^{(k)}$$

Pada saat t = 0 saat  $SC_1$  pertama kali tertutup maka:

$$I_2 = \frac{VC_2}{R_2} = \frac{V_{O2}}{R_2};$$

dimana tegangan awal  $V_{O2} = VC_2$ Dari persamaan (2.3) pada saat t = 0 diperoleh:

$$I_2 = e^{-(\frac{0}{R_2C_2})} e^{(k)} = \frac{V_{O2}}{R_2}$$

atau

$$e^{(k)} = \frac{V_{O2}}{R_2}$$

Sehingga fungsi arus  $I_2$  terhadap waktu dari persamaan (2.3) menjadi :

$$I_2(t) = \frac{V_{O2}}{R_2} e^{-(\frac{t}{R_2 C_2})}$$

(2.4)

dan fungsi tegangan terhadap waktu dari persamaan (2.4) menjadi:

$$V_{2}(t) = R_{2}.i_{2}(t) = R_{2}.\frac{V_{O2}}{R_{2}}.e^{-(\frac{t}{R_{2}C_{2}})}$$

$$V_{2}(t) = V_{O2}.e^{-(\frac{t}{R_{2}C_{2}})}$$

(2.5)

dengan penurunan rumus yang sama dimana  $VC_1 = VO_1 = V_S - 0.7$  didapat nilai perhitungan  $I_1(t)$  dan  $V_1(t)$  menjadi:

$$I_{1}(t) = \frac{V_{s} - 0.7}{R_{1}} \cdot e^{-(\frac{t}{RIC_{1}})}$$

(2.6)

$$V_1(t) = (V_S - 0.7).e^{-(\frac{t}{R_1C_1})}$$

(2.7)

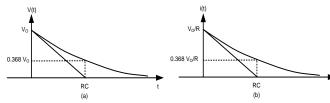

Grafik pengosongan kapasitor melalui R ditijau dari perubahan tegangan  $V_{1,2}(t)$  dan  $I_{1,2}(t)$  diperlihatkan pada Gambar.2 berikut [2]:

Gambar.2 Grafik pengosongan kapasitor melalui R ditinjau dari

a)Tegangan  $V_{1,2}(t)$  dan b) arus  $I_{1,2}(t)$  [2]

### Faktor ripple dan Bypass Filter kapasitor

Switching power supply memiliki tegangan ripple melebihi 500 mV diatas ambang noise yang diperbolehkan untuk mikrokontroler, maka perlu dipasang kapasitor untuk mengurangi faktor ripple dari tegangan power supply. Faktor ripple adalah figure of merit (bilangan yang digunakan untuk perbandingan) untuk catu daya yang dapat diformulasikan sebagai berikut [3]:

$$r = \frac{v_r}{v_{dc}}.100\%$$

(2.8)

di mana v<sub>r</sub> adalah nilai dari *ripple* efektif, dan v<sub>dc</sub> tegangan keluaran DC faktor *ripple* yang dihasilkan *switching* sangat buruk, sehingga untuk menghilangkan *ripple* tersebut, perlu dipasang kapasitor filter pada frekuensi jala-jala listrik 50 Hz

(Indonesia). Panjang waktu (perioda) dari frekuensi 50 Hz adalah sebesar:

$$T = \frac{1}{f} = \frac{1}{50Hz} = 20ms$$

(2.9)

Agar mempunyai konstanta waktu yang panjang, R<sub>L</sub>C harus jauh lebih besar dari 20 ms. Paling sedikit 10 kali, yaitu [3]:

$$R_LC \ge 20ms$$

(2.10)

Dimana  $R_L$ = tahanan dalam beban; C = filter kapasitor

Kapasitansi minimum filter kapasitor agar bisa meredam *ripple* dapat dihitung dengan formula [3]:

$$C_{\min} = \frac{0.24}{rR_{L}}$$

(2.11)

### Transistor Sebagai Pengendali Relay

Transisitor dikenal juga dengan *bipolar junction transistor* (*BJT*), merupakan suatu komponen semikonduktor penguat arus. *BJT* terdiri dari dua tipe yaitu NPN dan PNP.

Pada penelitian ini digunakan transistor hanya jenis NPN saja. Arus akan mengalir hanya jika diberi bias positif pada pin basis (B) dan arus penguatan akan mengalir dari collector (C) ke emitor (E), pada penguat switch (on-off) arus kolektor ( $I_C$ ) mendekati arus emiter ( $I_E$ ), dimana arus basis ( $I_B$ ) dapat dikuatkan dengan persamaan rumus[4]:

$$I_E \approx I_C = I_B.\beta$$

(2.12)

Dimana  $\beta$  adalah penguatan DC dari transistor tersebut, nilai  $\beta$  biasanya antara 100-200.

Transistor akan aktif sebagai saklar apabila diberikan arus pada basis transistor sebesar :

$$I_{B} = I_{B \text{ (saturasi)}}$$

(2.13)

Saat kondisi saturasi, transistor seperti sebuah saklar yang tertutup yaitu kondisi on, sehingga arus dapat mengalir dari kolektor menuju emitor dimana tegangan antara kolektor dan emitor ( $V_{CE}$ )

mendekati nol. Sedangkan saat kondisi *cutoff*, transistor seperti sebuah saklar yang terbuka yaitu kondisi *off*, sehingga tidak ada arus yg mengalir dari kolektor ke emitor dimana tegangan antara kolektor emitor  $(V_{CE})$  sama dengan tegangan catu  $(V_{SS})$ .

Beberapa hal yang harus diperhatikan agar transistor dapat berfungsi sebagai saklar diantaranya adalah menentukan  $I_C$ .  $I_C$  adalah arus beban yg akan mengalir dari kaki kolektor ke emitor. Besarnya arus beban ini tidak boleh lebih besar dari  $I_C$  maksimum yang dapat dilewatkan oleh transistor. Arus beban ini dapat dicari dengan persamaan berikut [4]:

$$I_{C(beban)} < I_{C(maksimum)}$$

$$(2.14)$$

$$I_{C(beban)} = \frac{V_{SS}}{R_{beban}}$$

$$(2.15)$$

Setelah arus beban yg akan dilewatkan pada transistor telah diketahui maka selanjutnya adalah menentukan transistor yg akan dipakai dengan syarat seperti berikut :

$$\beta > 5X \frac{I_{C(beban)}}{I_{C(maksimum)}}$$

(2.16)

Selanjutnya adalah menentukan hambatan pada basis  $(R_B)$ . Besarnya  $R_B$  ini dapat dicari dengan persamaan berikut [4]:

$$I_{B} = \frac{I_{C(beban)}}{\beta}$$

(2.17)

$$R_{B} = \frac{V_{BB} - V_{BE}}{I_{B}} \quad \text{dan } V_{BE} = 0.7V$$

(2.18)

$$V_{CE} = V_{C} - V_{E} = V_{SS} - I_{C}.R_{C}$$

(2.19)

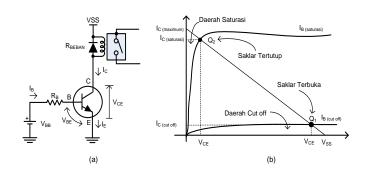

Rangkaian pengendali relay dengan BJT berikut titik kerja transistor sebagai saklar diperlihatkan pada Gambar.3 berikut [4]:

Gambar.3 (a) Rangkaian BJT, (b) Grafik titik kerja saturasi dan *cutt off* [4].

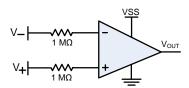

#### Opamp sebagai pembanding tegangan

Opamp memiliki penguatan tegangan (A) yang sangat besar, walaupun sangat besar nilai penguatannya dibatasi oleh besar sumber tegangan. Opamp sebagai pembanding tegangan diformulasikan sebagai [5]:

$$V_{OUT} = A(V_{+} - V_{-})$$

(2.20)

Dimana A= penguatan opamp tak hingga (penguatan loop terbuka), V<sub>+</sub> tegangan masukan pada pin *non inverting*, V<sub>-</sub> tegangan masukan pada *pin inverting*. Rangkaian opamp sebagai pembanding tegangan diperlihatkan pada Gambar.4 berikut [5].

Gambar.4 Rangkaian opamp sebagai pembanding tegangan

Tegangan keluaran (V<sub>OUT</sub>) dapat diformulasikan sebagai:

bila

$$V_{+} > V_{-}$$

maka  $V_{OUT} = V_{SS}$  (2.21)

bila  $V_{+} < V_{-}$  maka  $V_{OUT} =$  Ground (0 Volt) (2.22)

Opamp memiliki impendansi input yang sangat besar bahkan tak terhingga, hampir dipastikan arus yang masuk pada setiap pin masukan (pin *inverting* dan pin *non inverting*) adalah sama dengan nol Ampere. Penempatan resistor disetiap pin masukan, memberikan kontribusi sebagai proteksi arus lebih dan memperbaiki kinerja impedansi masukan opamp. Sebaliknya impedansi keluaran opamp V<sub>OUT</sub> sangat kecil sekali dan mendekati hubung singkat [5].

#### METODE PENELITIAN

Dalam tulisan ini, metode penelitian akan dititik beratkan pada sistem rangkaian proteksi *power supply*, dengan langkah metode penelitian:

- a. Menganalisa hubungan antara rangkaian seri RC dari fungsi step tegangan searah (DC) terutama dalam sistem pengosongan kapasitor, hasil pengamatan dan perhitungan dituangkan dalam tabel pengamatan.

- b. Menganalisa hubungan rangkaian seri RC dengan sistem kompensasi suhu, waktu tunda, dan faktor *ripple* tegangan, terutama dalam hal pemilihan komponen elektronika yang tepat dan efisien terhadap kecepatan waktu tanggap dan kinerja.

- c. Hasil pengamatan dan analisa akan dijadikan fitur ideal prototipe dalam hal proteksi dan dapat diterapkan modul praktikum lainnya.

# RANCANG BANGUN HASIL DAN PEMBAHASAN

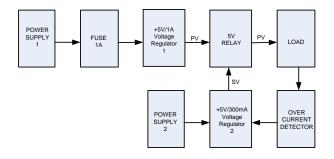

Pada Gambar 5 diperlihatkan diagram blok sistem proteksi *power supply* konvensional dengan 2 buah power supply dan fuse pada keluaran power supply utama.

Gambar.5 Sistem proteksi power supply konvensional

Power supply dipecah kedalam dua voltage regulator, +5V/1A voltage regulator 1

diperuntukan untuk primary voltage (PV) yang memenuhi kebutuhan arus dan tegangan komponen uji (protoboard), alat ukur dan display, yang semuannya menjadi beban (LOAD) dari +5V/1A voltage regulator 1 melalui ialur PV. +5V/300 mA voltage regulator 2 diperuntukan untuk secondary voltage (SV) untuk memenuhi kebutuhan arus dan tegangan relay 5V saja. Metode ini diharapkan apabila terjadi over current pada beban (short circuit), maka tegangan di +5V/300 mA voltage regulator 2 tidak drop sehingga relay akan bekerja (on) untuk mematikan jalur PV. Metode proteksi power supply konvensional ini tidak berhasil karena pada saat short circuit tegangan PV lebih cepat jatuh (transient) ke ground sehingga fuse lebih cepat putus dibandingkan dengan aktifasi relay, akibatnya fuse sering diganti (tidak efisien).

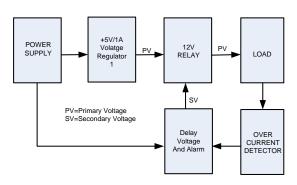

Untuk memperbaiki kesalahan dari metode proteksi power supply konvensional ini dibuatlah metode single voltage regulator with time delay protection and alarm seperti diperlihatkan pada Gambar.6.

Gambar.6 Sistem proteksi power supply dengan metode single voltage regulator with time delay protection and alarm

Metode ini mengunakan hanya satu *voltage regulator* utama +5V/1A yang telah dimodifikasi dengan rangkaian tunda dan alarm. Apabila terjadi hubung singkat dijalur PV maka jalur SV akan dipertahankan beberapa *milli second* (ms) untuk menghidupkan relay, memutus jalur PV dan menghidupkan alarm (peringatan hubung singkat), rangkaian ini tidak memerlukan *blow up fuse* karena hubung singkat beberapa *milli second* tidak akan merusak *power supply* utama.

Selama *power supply* di protoboard masih terjadi hubung singkat, maka alarm akan tetap dipertahankan berbunyi dan *power supply* dalam keadaan aman (terkunci), jalur PV akan disalurkan kembali apabila bagian yang terhubung singkat telah dinetralkan. Rangkaian sistem proteksi *power* supply dengan metode single voltage regulator with time delay protection and alarm diperlihatkan pada Gambar 7.

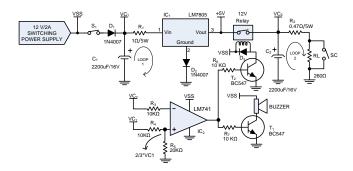

Gambar.7 Sistem proteksi power supply dengan metode single voltage regulator with time delay protection and alarm

$D_3$  sebagai proteksi dari arus berlebih (*Snubber*) sebagai akibat efek induksi magnetik akibat bukatutup coil relay.  $C_2\text{-}R_2$  adalah rangkaian penunda waktu (pengosongan kapasitor), pada saat  $R_L$  terjadi hubung singkat ( $R_L$ =0 $\Omega$ ) dengan loop arus tegangan 2 berturut-turut  $I_2(t)$  dan  $V_2(t)$  dicari dengan persamaan (2.4) dan (2.5). Nilai transien perubahan tegangan  $V_2(t)$  diperlihatkan pada Tabel.1 .

$C_1-R_1$ adalah rangkaian penunda (pengosongan kapasitor), pada saat  $R_L$  terjadi hubung singkat ( $R_I=0\Omega$ ). Terjadi drop tegangan pula pada tegangan masukan di pin 1 voltage regulator IC<sub>1</sub>. Drop tegangan sesuai dengan transient pengosongan kapasitor  $C_2$ - $R_2$ Pengosongan kapasitor C<sub>1</sub> terjadi penunda waktu dengan loop arus tegangan 1 berturut-turut I<sub>1</sub>(t) dan V<sub>1</sub>(t) dicari dengan persamaan (2.6) dan (2.7). Nilai transien perubahan V<sub>2</sub>(t) diperlihatkan pada Tabel.2

Dari Tabel 1 diperlihatkan penurunan tegangan 3 dB  $(0.5\ Vo)$  dari  $V_2(t)$ , terjadi pada waktu pengosongan  $0.8\ ms$ , sedangkan dari Tabel.2 penurunan tegangan 3dB (0.5Vo) dari  $V_1(t)$ , terjadi pada waktu pengosongan  $1.4\ ms$ . Ini membuktikan bahwa waktu pengosongan  $R_1\text{-}C_1$  jauh lebih lambat daripada waktu pengosongan  $R_2\text{-}C_2$ . Kecepatan transient waktu pengosongan (tunda) tergantung pada nilai  $R_1$  dan  $R_2$ .

R<sub>1</sub> dan R<sub>2</sub> dipilih dengan nilai sangat kecil agar tidak membebani *power supply* utama.

Tabel 1 Nilai transient perubahan tegangan V<sub>2</sub>(t)

| waktu | -t/R2C2   | Vo     | V <sub>2</sub> (t) |

|-------|-----------|--------|--------------------|

|       | R2=0.47W  |        |                    |

| (ms)  | C2=2200uF | (Volt) | (Volt)             |

| 0.1   | -0.10     | 5.7    | 5.17               |

| 0.2   | -0.19     | 5.7    | 4.70               |

| 0.3   | -0.29     | 5.7    | 4.26               |

| 0.4   | -0.39     | 5.7    | 3.87               |

| 0.5   | -0.48     | 5.7    | 3.51               |

| 0.6   | -0.58     | 5.7    | 3.19               |

| 0.7   | -0.68     | 5.7    | 2.90               |

| 0.8   | -0.77     | 5.7    | 2.63               |

| 0.9   | -0.87     | 5.7    | 2.39               |

| 1     | -0.97     | 5.7    | 2.17               |

Tabel.2 Nilai perubahan tegangan V<sub>1</sub>(t)

| 1.    | -t/R1C1   | V <sub>o</sub> | $V_1(t)$ |

|-------|-----------|----------------|----------|

| waktu | R1=1W     |                |          |

| (ms)  | C1=2200uF | (Volt)         | (Volt)   |

| 0.1   | -0.05     | 11.3           | 10.80    |

| 0.2   | -0.09     | 11.3           | 10.32    |

| 0.3   | -0.14     | 11.3           | 9.86     |

| 0.4   | -0.18     | 11.3           | 9.42     |

| 0.5   | -0.23     | 11.3           | 9.00     |

| 0.6   | -0.27     | 11.3           | 8.60     |

| 0.7   | -0.32     | 11.3           | 8.22     |

| 0.8   | -0.36     | 11.3           | 7.86     |

| 0.9   | -0.41     | 11.3           | 7.51     |

| 1.0   | -0.45     | 11.3           | 7.17     |

| 1.1   | -0.50     | 11.3           | 6.85     |

| 1.2   | -0.55     | 11.3           | 6.55     |

| 1.3   | -0.59     | 11.3           | 6.26     |

| 1.4   | -0.64     | 11.3           | 5.98     |

| 1.5   | -0.68     | 11.3           | 5.71     |

|       | ·         |                |          |

IC<sub>2</sub> akan membandingkan waktu tunda penurunan tegangan kapasitor dari VC<sub>1</sub> dan VC<sub>2</sub>. Pada saat *standby* (normal) keluaran IC<sub>2</sub> akan selalu 0 volt (ground), karena V- selalu lebih besar dari V+

(VC1>2/3\*VC2) sesuai persamaan (2.22). tetapi sebaliknya pada saat terjadi hubung singkat di RL,

$VC_1$  akan selalu lebih kecil dibandingkan dengan  $VC_2$  mengakibatkan keluaran selalu positip (VSS) sesuai persamaan (2.21), mengakibatkan transistor  $T_1$  dan  $T_2$  aktif, sehingga buzzer akan bunyi dan relay akan 'on' dan memutuskan jalur PV ke beban RL sesuai persamaan (2.19). Relay akan tetap on (terkunci) sampai saklar  $S_1$  dilepas. Relay akan 'off' dan buzzer akan berhenti hanya apabila lokasi hubung singkat telah dinetralkan, dan saklar  $S_1$  telah ditutup kembali.

Pada saat standby (tidak terjadi hubung singkat),  $C_1$  dan  $C_2$  berfungsi sebagai *bypass* filter. Dari hasil pengukuran, tahanan dalam rangkaian *main board* sebesar 260  $\Omega$ , sehingga  $C_{MIN}$  dapat dihitung minimal sesuai persamaan (2.11):

$$C_{\min} = \frac{0.24}{rR_{L}} = \frac{0.24}{4.16 \times 260} = 2200 uF$$

Agar ripple dapat dikurangi, maka  $C_1$  dan  $C_2$  dipasang optimal minimal sebesar 2200 uF dengan faktor ripple AC kurang dari 1%.

Foto hasil penelitian prototipe secara keseluruhan diperlihatkan pada Gambar.8 berikut:

Gambar 8. Foto prototipe hasil penelitian

Foto *mainboard* hasil penelitian diperlihatkan pada Gambar.9, tanda lingkaran menunjukan bagian sistem proteksi *power supply*.

Gambar 9. Foto *mainboard* prototipe hasil penelitian, sistem proteksi *power supply* diperlihatkan dengan tanda lingkaran

#### **KESIMPULAN**

Beberapa analisa mengenai sistem proteksi *power* supply modul praktikum teknik digital dari hasil eksperimen dan penempatan prototipe dapat disimpulkan sebagai berikut:

- a. Penempatan R Shunt ( $R_1$  dan  $R_2$ ) dengan nilai antara  $0.5\Omega$ - $1\Omega$  (5W) sangat efektif terhadap penyaluran arus listrik, pengosongan kapasitor dan kompensasi suhu akibat desipasi daya yang diserap oleh beban. Suhu berlebih akan disalurkan kepada R Shunt ini sehingga mengurangi resiko kerusakan sumber daya aktif lainnya.

- b. Penempatan kapasitor (C<sub>1</sub> dan C<sub>2</sub>) dengan nilai

22.000 uF/16V dapat mengurangi *ripple factor* AC kurang dari 1% (*bypass filter*).

- c. Sistem proteksi menggunakan teknis waktu tunda (pengosongan kapasitor) dan sistem pembanding tegangan opamp mampu mendeteksi adanya hubung singkat rangkaian beban pada orde kurang dari 5 ms (0.1ms-1.5 ms), sehingga teknis penyelamatan *power supply* lebih baik.

- d. Ditunjukan pula proteksi menggunakan metode single voltage regulator with time delay protection and alarm, mampu memberi efektivitas tinggi baik dari segi pengamanan, kecepatan tanggap, peringatan, maupun cost produksi yang lebih berarti. Metode ini dapat diterapkan pada modul praktikum lainnya.

#### **DAFTAR PUSTAKA**

- [1] "Revolusi industri dan revolusi digital", 2013. [online]. Available : <a href="http://www.beritateknologi.com/">http://www.beritateknologi.com/</a> [Accessed 20 Maret 2013].

- [2] M. Nahvi and J. A. Edminister, Electric Circuits, Schaum Series, Singapore: McGraw-Hill, 2010.

- [3] A. Malvino, Basic Electronics principles, Singapore: McGraw-Hill, 2010.

- [4] T. L. Floyd, Electronics Fundamental Circuits, Devices, and Application, Winkler: P.9, 2012.

- [5] R. A. Gayakwad, Op-Amps and Linear Integrated circuits, US Imports & PHIPES, 2011.